Предположив, что читатель уже знаком с теорией и практикой энергоэффективных и дешёвых процессоров на примере Intel Atom, статью о VIA Nano мы построим по принципу поиска ответов на вопрос: «Почему VIA сделала это не так, как Intel?» Но сначала давайте попытаемся понять, что́ она вообще хотела.

То, что выпускаемые компанией до сих пор процессоры C7 и Eden давно устарели по всем параметрам — ясно без всяких обзоров. То, что новое решение в случае удачи будет популярно, ясно по активности продаж Атома (правда, у VIA нет такого отдела маркетинга…). Также понятно, что делать процессор для серверов VIA просто «не потянет» (да и одним процессором не обойдёшься, нужна платформа целиком), а выпускать сегодня CPU для стандартных десктопов бессмысленно: в этом секторе и так не протолкнуться, к тому же там есть AMD со своей привычкой чуть что демпинговать почти на уровне себестоимости. А вот Intel мало того, что потянет практически всё, что угодно — так ещё и активно рвётся во все стороны, где ещё «не ступала нога» платформы x86 её производства, зато вполне присутствует VIA — это компактные платы для встроенных решений и экономных компьютеров в разных форм-факторах. Таким образом, решение о кардинальном обновлении своей линейки сильно упрощённых процессоров VIA Technologies откладывать было нельзя.

До тех пор VIA придерживалась таких правил: с 0,4 по 1 ГГц мы должны быть круче всех; с 1 по 1,5 ГГц — конкурировать с переменным успехом с «низами» Intel и AMD; а всё, что выше 1,5 ГГц — не для нас. Но парадигму надо было менять. Сегодня, задним числом, мы можем предположить, что́ нужно было сделать VIA, чтобы результат имел шансы хотя бы на паритет с возможным конкурентом. Итак, пока Intel экспериментировала с крайностями, VIA был нужен ЦП:

- Достаточно быстрый — стабильно быстрее Атома и ненамного медленнее последних на момент своего выпуска Core 2 и K8 (с одинаковыми частотой и числом ядер);

- Достаточно экономный — в карманные устройства его никто вкладывать не собирался (для этого VIA заказывает ЦП с ARM-ядрами), зато в остальных почти всегда можно обойтись лишь общим радиатором с чипсетом;

- Достаточно дешёвый — на деле Нано стоит от $35 за 1 ГГц, но (как и остальные решения VIA) продаётся впаянным в плату своего производства на своём же чипсете — за $70–150 (как у дешёвых плат с Атомами).

Т. е. нужен был просто хорошо сбалансированный ЦП средней сложности, который окажется «всего лишь» в 2–4 раза быстрее предыдущих — при тех же частотах, ваттах и долларах. Intel позволила Атому быть очень медленным в угоду экономии и дешевизне, для чего двинулась назад и выбрала как пример свою же давно заброшенную архитектуру 15-летней давности. VIA сама до сих пор имеет подобный раритет, сделанный купленной Centaur Technology (произносится «Синтор»). Так что, с одной стороны, её инженерам не понадобилось ничего вспоминать, с другой же — им нужно было резво вырваться вперёд, быстро сделав работу, выполненную инженерами Intel и AMD за 5-10 лет до этого.

Производить ЦП самим Centaur или VIA не нужно — за них это делают Fujitsu (на техпроцессе 65 нм) и TSMC (на 90 нм), так что от сложности микроэлектронных оптимизаций их избавил бесфабричный статус (fabless). Но учитывая, что Centaur — фирма небольшая (в 2004-м — 82 работника, включая тестеров и помощников, в 2008-м — около 100), задача всё равно получилась сложной. Кстати: фабрики производят только пластины — их резка и тестирование, а также сортировка и корпусировка чипов делается самой Centaur, причём с массой ручных операций и невысоким темпом…Как сделать x86-ЦП (за 5 минут для чайников)

Isaiah («Айзэя», таково имя архитектуры) разрабатывалась командой «кентавров» (Centaur формально остаётся отдельной фирмой, хотя полностью принадлежит VIA). Пересечения с «великой и ужасной» продолжаются и тут. Как мы помним, Intel отквартировала небольшую группку для работы над будущим Атомом в Остин, штат Техас — а именно там находится штаб Centaur (в компании он зовётся «кухней»). Более того, несколько бывших «кентавров» оказались в интеловской команде и вполне могли рассказать о готовящемся Isaiah (Атом начали разрабатывать чуть позже). Centaur же вряд ли знала об Атоме, иначе постаралась бы анонсировать Isaiah первой (даже до появления марки Nano) — но произошло это 24 января 2008-го, через 3 месяца после анонса Атома. Продажи Нано начались 29 мая, на месяц позже Атома.

Гленн Хенри описывает кристалл Нано.

Собственно над Isaiah работало 35 дизайнеров. Не считая трёх коллег, работающих вместе с главой Гленном Хенри в Centaur со дня её основания в 1994-м, другие поначалу не поверили, когда он предложил нанять ещё 20-30 профессионалов — было невероятно, чтобы такая малочисленная команда смогла сделать сколько-нибудь сложный ЦП. Хенри говорит, что главное в их успехе — узкая специализация конечного результата и комфорт в разработке. Альянс Centaur и VIA не пытается пропихнуть архитектуру x86 во все края и дали, а использует её именно там, где конкуренты пока не прижились, а у VIA до сих пор более-менее получалось. Ну а комфорт, по мнению главного «кентавра», даёт каждому инженеру производительность намного бо́льшую, чем в «крупной компании». Для этого им купили не только лучшие имеющиеся инструменты (программные и аппаратные), но и разработали собственные. Centaur гордится тем, что почти не увольняет работников — не за что и незачем, все всем довольны.

Вот пример: в Centaur есть дата-центр, где сотни мини-ПК на базе Pentium 4 и Core 2 круглосуточно эмулируют разрабатываемый ЦП на тысячах программ. Причём, несмотря на совсем не интеловский бюджет, Centaur не арендует дата-центр, а купила его по частям. На вопрос, что будет с этим железом, когда его возможностей перестанет хватать, и всё придётся менять на новое, Хенри ответил: «подарим сотрудникам».

Около 200 патентов красуются в холле компании.

Сразу после основания компании Гленн Хенри, до этого долго работавший на высоких постах в IBM и Dell, где управлял сотнями подчинённых, бегал по офисам производителей микросхем и говорил примерно так: «Нас 4 человека, дайте нам 15 миллионов долларов, оставьте в покое на пару лет, и мы вернём вам x86-ЦП. Зачем он вам? А затем, что микроэлектронная интеграция скоро позволит объединить на одном кристалле ЦП, кэш, чипсет и все контроллеры, так что ваши отдельные чипы покупать не будут, а купят интегрированный процессор — и с нашим ядром это может быть ваш процессор…»

Через год скитаний на это клюнула IDT, и через 2 года (в 1997-м) получила результат — WinChip C6. Ещё за 2 года Centaur успела выпустить 3 версии чуть обновлённого WinChip 2, после чего её перекупила VIA. Там «кентавры» всего за 5 лет родили 6 версий C3 и C7, отличавшихся от WinChip в основном размерами кэшей, степенью интеграции и внедрением очередного SSE*. Isaiah же требовал кардинального усложнения, а значит, и увеличения затрачиваемых ресурсов, поэтому на него потратили аж 4 года. VIA дала архитектуре библейское имя пророка Исайи (как и предыдущим решениям Centaur, например C7 Esther — Есфирь), а инженеры для себя назвали её CN (видимо, C-next) и делали её как бы с нуля, хотя по сути изобретали 3-колёсный 3-конвейерный велосипед — даром что название владельца расшифровывается как Very Innovative Architecture… Кстати, об именах: кодовое имя ядра Атома Bonnell — название холмика вблизи Остина, ну а VIA назвала «стряпню техасской кухоньки» именем минус девятой степени :) Ниже везде под VIA подразумевается Centaur.

Прежде чем описать архитектуру, скажем, что аппаратные счётчики событий, по показаниям которых можно исследовать ЦП, для Нано не документированы, и их привязка к событиям осуществлена почти наугад. Кроме того, в официальном описании архитектуры есть несколько нестыковок, хотя там всего 12 страниц. А ещё VIA всегда славилась преувеличением своих успехов и выпячиванием посредственных цифр как огромных достижений. Впрочем, не только она… :) Так что нижеописанное — частично спекуляция. Ещё один момент: уже в сентябре 2008-го VIA объявила о выпуске второй версии Isaiah — CNB (первую переименовали в CNA), что и произошло годом позже. Новые модели получили значительные улучшения.Фронт

VIA решила перепрыгнуть сама себя и от 1-конвейерного дизайна прошлых лет перешла сразу к 3-конвейерному. Допустим, что иначе существенный уровень производительности не получишь. Возникает вопрос: как сделать так, чтобы этот вариант оказался энергоэффективней пары ядер с двумя конвейерами или даже трёх-четырёх с одним? Ответ прост: если загрузить 3 конвейера одного ядра как можно полнее — и место, и прожорливость на каждую операцию у него будут куда меньше, чем у нескольких ядер, за счёт общих блоков (если всё сделать правильно…). Значит, главный вопрос — как загрузить конвейер так, чтобы сам механизм загрузки не оказался слишком сложным и жадным до энергии.

Как мы помним по обзору Атома, Интел решила, что механизм внеочередного исполнения (OoO) для 2-путного суперскаляра не подходит. Правда, и очерёдное исполнение сделано там неважно. Но для 3-путного решения этот вопрос даже не возникает — три одновременно исполняемые команды встретятся подряд куда реже, чем две. Именно это толкнуло Intel в 1995-м выпустить не просто первый (для x86) 3-путный суперскаляр, а с внеочередным исполнением — иначе, без подбора группы команд из нескольких десятков декодированных, 3 конвейера Pentium Pro не загрузишь. С другой стороны, обычный OoO-движок затратен по площади и ваттам. Так что перед VIA встала задача, похожая на ту, что решали авторы Pentium M — создать энергоэффективный OoO-процессор. А вот почему «кентавры» не рассмотрели SMT (у Intel — гиперпоточность) — не ясно… Кстати, Хенри открыто высказал непонимание и того, почему Intel вернулась к 2-поточному упорядоченному дизайну.

Предсказатель ветвлений в Нано весьма сложен: VIA говорит аж о 8 алгоритмах, включая механизм голосования для определения наиболее выгодного из остальных, исходя из их успешности для конкретной ветви — такой был в IBM Power4, Power5 и PPC970, но среди x86-ЦП это, вероятно, впервые (не считая сверхсекретных предсказателей в Pentium 4, о которых мало что известно). Если точнее, первая стадия предсказателя (до чтения из L1I) имеет 3 алгоритма для условных переходов (обычный типа If-Then, эпилог цикла и ещё один, возможно, для «стабильных» ветвей), «избиратель» из них и предсказатель адреса возврата. Вторая стадия (работает параллельно с декодером) имеет предсказатели «лишних» возвратов, «лишних» условных ветвлений и статический, действующий для впервые встреченных или «забытых» переходов. Вторая стадия иногда замещает своим предсказанием мнение первой.

Основной буфер адресов перехода (BTB, по терминологии VIA — BTAC) находится в первой стадии, имеет 4096 ячеек и организован как 4-путный наборно-ассоциативный. Как в процессорах AMD, он имеет фиксированную связь с кэшем L1I — на каждые 16 байт кода приходится в среднем одна ячейка BTB, но не более двух. Не умещающиеся тут адреса складываются в дополнительном буфере на 2048 ячеек для «лишних» предсказателей.

По результатам независимого анализа, основной предсказатель условного перехода ведёт себя примерно как адаптивный 2-уровневый с 12-битными локальными историями каждого перехода и 2-битной глобальной историей всех переходов. Цифры весьма странные, т. к. обычно баланс разрядностей выбирается обратный — 8-16 бит для глобальной и 0-4 для локальной. Официальный документ таких деталей не раскрывает (а регистры локальной истории вообще не упоминает, так что их может и не быть), но пишет, что 4 12-битных индекса, образуемые сливанием глобальной истории (неуказанной длины) и части битов адреса 16-байтового блока, адресуют 4 таблицы для 4 основных алгоритмов, причём 4 функции слияния — разные.

В каждой таблице — 4096 пар 2-битных счётчиков поведения предполагаемых в выбранном блоке переходов, включая безусловные. Если там есть и регистры локальных историй — место в них резервируется в зависимости от числа переходов в блоке: если переход один — ему выделяются все биты, если два — каждому по половине (хотя если один из пары всегда срабатывает, то качество предсказания второго почему-то особенно плохо), а если больше двух — для остальных используются «лишние» предсказатели, которые медленней и глупей.

Предсказатель эпилогов циклов верно срабатывает при 15–20 итерациях, если в цикле нет других переходов, и при 12–16, если они есть (что хуже, чем счётчик на 64 итерации в Pentium M и Core 2/i). Косвенные переходы всегда предсказываются как переходящие по последнему сработавшему для них адресу (т. е. специального алгоритма или буфера, как в K10, для них нет). Стек адресов возвратов показан на официальной схеме, но как отдельный блок может и отсутствовать, храня адреса в BTB — только так можно объяснить то, что, в отличие от других ЦП с их фиксированными стеками на 12–24 ячейки, Нано умеет предсказывать возвраты даже из рекурсивных процедур большой вложенности.

Общий алгоритм первой стадии таков: 3 основных предсказателя дают свои заключения мажоритару, выбирающему мнение большинства. 4-й предсказатель является диктатором, решение которого полностью соответствует известной фразе, приписываемой Иосифу Сталину — «Важно не как голосуют, а как подсчитают»: либо использовать результаты «демократии трёх голосов», либо авторитетное мнение только первого алгоритма для наиболее общего случая условных переходов. Результат поведения комбинируется с целевым адресом, получаемым из BTB или стека возврата (если он есть).

При неверном предсказании штраф — 16 тактов (иногда до 20); это на 3 больше, чем у Атома, и косвенно говорит о длине всего конвейера. Предсказатель всегда ошибается, если после перехода (даже безусловного) находится так называемая сериализующая команда, требующая опустошения конвейера от других, уже запущенных команд до исполнения себя — впрочем, встречаются они редко. Несмотря на 2-стадийную схему темп предсказателя — 1 переход за 3 такта (в др. ЦП — за 2), чего может не хватить при исполнении трёх команд/такт. Сами переходы срабатывают за 3 такта, проходятся за 1, а если их более двух в блоке, то каждый, начиная с третьего, требует 8 тактов при любом поведении.

Считывание из L1I, как уже ясно, происходит 16-байтовыми блоками, чего вполне хватит для 3-путного суперскаляра (в 4-путных Core 2/i те же 16 байт/такт). Блоки (без буферизации, как в др. ЦП) поступают в предекодер-длиномер, размечающий до трёх команд/такт вне зависимости от их сложности, длин и числа префиксов (включая избыточные) — главное, чтобы первые байты команд, достаточные для определения их длины, уместились в блоке (последняя команда может за него и выйти). Всё это сильно выдаётся на фоне ограничений по префиксам у всех остальных ЦП, особенно учитывая отсутствие буфера разметки. После длиномера есть FIQ (Formatted Instruction Queue) — очередь из 16 команд, «отформатированных» на компоненты примерно так: тег префиксов, коды операции и операндов, 3 регистра, константа и адрес (расширенные до полной разрядности). В Core 2/i такая очередь имеет 18 команд.

Предекодер Нано оснащён механизмом макрослияния (mаcrofusion), имеющим такие правила:

- Первая команда должна быть простой арифметической или логической, исполняемой скалярным АЛУ, всего — 9 типов. Для сравнения — для Core 2/i подойдут лишь команды сравнения и логического теста;

- Аргументы первой команды должны быть регистрами, но не памятью или константой;

- В CNA вторая команда может быть лишь JE или JNE (или её синонимы — J(N)Z), в CNB — любая, кроме случая проверки флага переноса, если он не изменён первой командой. Похожий прогресс был от Core 2 до Core i;

- В CNB «пустышка» NOP сливается с почти любой предыдущей командой, а если после неё есть ещё одна «удачная» инструкция, подходящая по критериям выше — то и с ней. Это касается и многобайтового НОПа, но не вещественного (др. ЦП и так не умеют).

Заметим, что все правила действуют и в 64-битном режиме, тогда как у Core 2 макрослияние в нём недоступно (что исправлено в Core i). Однако Нано не умеет «добирать» лишнюю команду — в отличие от Core 2/i, где макрослияние увеличивает число декодированных команд на одну (а максимума за такт — до пяти), тут максимум остаётся на уровне трёх.

Форматированные команды поступают в 3-путный декодер, состоящий из микросеквенсора с микрокодом и трёх сложных трансляторов, каждый из которых может генерировать 1–3 мопа, в т. ч. «микрослитые» (у др. ЦП сложный транслятор лишь один, а у Атома — ноль). Микрокод имеет ПЗУ на 8192 тройки мопов и может быть обновлён однократно прожигаемыми перемычками (на схеме чипа — Fuses). Микросеквенсор имеет собственный механизм переходов (включая условные) и даже вызовов «подмикропрограмм» — эти команды исполняются прямо в нём, а не в исполнительной части.

С совместимостью у декодера всё в норме — все Нано поддерживают x86-64 и векторные команды вплоть до SSSE3, а CNB — и SSE4.1 (т. е. по архитектурной «всеядности» VIA переплюнула K8/K10 и Atom и достала до Core 2). Виртуализация, как выяснилось позже, поддерживалась с самого начала, но была отключена (видимо, из-за ошибок) — активировали её в CNB и в степпинге 3 у CNA.

После декодера есть очередь мопов неизвестного размера. Механизма обнаружения и блокировки циклов (как в Core 2/i) в ней нет, зато в неё не попадают команды из микрокода — они сразу направляются в OoO-часть, пока очередь копит оттранслированные мопы, готовые к отправке сразу после завершения микропрограммы (кроме случая встречи другой микрокодовой команды).Тыл

OoO-механизм, включая переименование регистров и отставку, работает с темпом 3 мопа/такт и грубых промахов, как планировщик Атома, не допускает. Например, команды обмена регистров стека x87 и его прокрутки не доходят до исполнения — их «сокращают» при переименовании регистров. Остальные одновременно попадают в ROB (OoO-буфер) и распределяются по семи «резервационным станциям» (RS). Длина ROB — более 76 мопов (возможно, 84 — должно делиться на 7), что больше 3-путных архитектур AMD (72) и, видимо, отстаёт от Core 2/i (96 и 128). Кстати, ROB неудачно называют буфером переупорядочивания (ReOrder Buffer): на самом деле его задача — хранить до отставки оригинальный порядок мопов, причём слитых.

Имея неодинаковый размер, в сумме 7 RS Нано хранят 76 мопов. Сравним: в Core i — общая резервация на 36 мопов, у AMD K8/K10 — общая для вещественно-векторных ФУ и 3 для целочисленных (36+3x8 мопов). В Нано каждый слитый моп регистрируется в паре RS. В любую RS могут попасть до трёх мопов/такт, а запускаются из неё они по одному, обеспечивая непрерывную загрузку ФУ (у AMD планировщик добавляет в поток выравнивающие затычки-«пузыри»).

В Нано 7 портов, объединяющих ФУ в исполнительные кластеры (сами ФУ рассмотрим позже):

| Порт | Команды в CNA | Изменено в CNB |

| I1 | Целая скалярная арифметика, логика и сдвиги | + копирование |

| I2 | Целая скалярная арифметика и логика, копирование, переходы | + простые сдвиги и умножения до 32 бит |

| MB | Все умножения | Целые скалярные умножения — только 64-битные (остальные в I2) |

| MA | Остальные вещественные и/или векторные операции, деления всех видов и шифрование | |

| SA | Вычисление адреса для записи и команды LEA | |

| ST | Запись в память | |

| LD | Чтение из памяти |

Почти недостижимый максимум числа запусков мопов за такт — 7, из которых до четырех — вычислительные, что даже лучше, чем у Core 2/i. Как и в Атоме, можно без штрафов смешивать разные по длительности команды в одном порту, но для этого они должны исполняться на разных ФУ. Есть и недостатки: когда RS обоих целочисленных портов заполнены, диспетчер отправляет все накопленные там мопы только в I1. В CNA 1-байтовые НОПы «исполняются» буквально, причём блокируя все порты (исправлено в CNB). А ещё при загрузке из памяти регистры-указатели блокируются на 4 такта (видимо, связанно с задержкой L1D).

Запись в память декодируется в слитый моп (для адреса и самой операции), запускаемый в SA и ST (у Intel слитые записи появились в Pentium M). Для чтения адрес, видимо, вычисляется в том же LD, но обычным мопом. А вот микрослияния для чтения-модификации или хотя бы чтения-исполнения нет — эти команды требуют 3 и 2 мопа соответственно, тогда как у Core 2/i — 2 и 1, а у Atom и AMD — 1 и 1.

Передача результатов между портами занимает 0–2 такта, что ожидаемо для современного ЦП. Поэтому смешивать команды для разных видов данных не следует, даже если они делают одно и то же (например POR, ORPS и ORPD — векторное логическое ИЛИ) — а именно это допускают компиляторы для экономии размера кода (PS-версии команд на 1 байт короче остальных), приводя к штрафу в 4–5 тактов. Нано не штрафует, только если данные не меняются, а лишь копируются.

OoO ЦП часто страдают от дополнительных задержек при частичном доступе к регистру — когда одна команда что-то пишет в часть регистра, а следующая (не обязательно подряд) читает его весь. Т. к. данные чаще передаются напрямую от ФУ к ФУ через шлюзы перепуска с одновременной записью в регистровый файл, прочесть обновлённую версию регистра оттуда можно только после завершения записи. Как ни странно, в Нано ничего подобного не наблюдается — видимо, порты перепуска умеют комбинировать считанные из РФ и из шлюза части операнда. Но это вносит ложные взаимозависимости по операндам: например, запись в младшую половину регистра вынуждена ждать окончания предшествующей записи этого регистра целиком (в других ЦП эта проблема иногда решена для РОНов). А вот флаги ведут себя прямо противоположным образом: отдельные биты и их группы могут свободно комбинироваться при записи, но при немедленном чтении хотя бы нескольких битов происходит задержка аж в 7 тактов.

Как известно, в архитектуре x86 нет отдельной команды для обнуления регистра — вместо этого чаще всего используют инструкцию вида XOR R,R (т. е. исключающее ИЛИ регистра с собой). Однако это вносит ложную зависимость — с точки зрения диспетчера, команда дважды читает некий регистр, а затем что-то в него пишет, да ещё и обновляет флаги. В реальности же результат всегда предопределён. Поэтому процессоры давно научились отделять некоторые виды команд (если их операнды одинаковы) в отдельные мопы, которые только пишут константы и не читают предыдущее состояние. CNA распознаёт наиболее частые подобные случаи, а CNB — и большинство других, но не все.

У всех процессоров VIA начиная с C3 есть особый набор команд PadLock и аппаратные блоки для них — они используются для (де)шифрования по стандартам AES и RSA, вычисления контрольных сумм SHA и генерации истинных (а не псевдо-) случайных чисел (ГСЧ). Совсем недавно Intel внедрила в Core i похожий набор AES-NI, но там ускоряется лишь (де)шифрование AES (CNB для совместимости включил в себя и эти команды). Прямое сравнение этих поднаборов пока не приведено, но VIA утверждает, что ЦП Eden-N (ядро C7) на 1 ГГц обгоняет Pentium 4 на 2,4 ГГц в 4–150 раз при шифровании с использованием PadLock.

В CNA задержки этих команд — 44–63 такта на каждые 16 байт. ГСЧ работает ещё медленнее: генератор использует шумовые неравномерности частоты накристальных осцилляторов, для замера чего нужно 1300–19200 тактов в зависимости от требуемого качества «случайности» генерируемых 64 бит. Впрочем, этот блок работает независимо от остальных и считывает во внутренний 8-байтовый буфер очередную порцию «хаоса», немедленно доступную по команде. Криптографы уже протестировали ГСЧ в CNA известным набором тестов Diehard — при высоких значениях качества Нано прошёл все тесты, при низких — не все, зато куда быстрее :) CNB ускорил ГСЧ до 1300–5500 тактов на 8 байт, шифрование до 15–37 тактов на 16 байт, но хэширование чуть замедлилось до 5 тактов/байт. Независимый тест PadLock показывает вот что (x86-ЦП принудительно замедлены, результаты нормализованы относительно ядра ARM): Числогрыз

Числогрыз

Самое интересное в Нано — это функциональные устройства, а точнее, их темп в тактах. Если усреднить, таких низких значений не имеет ни один современный x86-ЦП. Продемонстрируем это уже знакомой, но обновлённой таблицей задержек/пропусков. В этой версии худшее и лучшее значения каждой строки, если они в ней одни, выделены красным и синим соответственно. При этом значения для CNB указаны как улучшающие CNA, так что у этой пары допустимы две цветных клетки; тёмно-зелёные цифры пока проигнорируем:

| Домен | Действие | Команды | Atom | P II, III | P M | Core 2 | Core i | K7 | K8 | K10 | CNA | CNB |

| Скалярный целочисленный | Копирование | MOV | 1/0,5 | 1/0,5 | 1/0,5 | 1/0,3 | 1/0,3 | 1/0,3 | 1/0,3 | 1/0,3 | 1/1 | 1/0,5 |

| Условное копирование | CMOV* | 2/2 | 1/1 | 2/1,5 | 2/1 | 2/1 | 1/0,3 | 1/0,3 | 1/0,3 | 2/1 | 1/0,5 | |

| Обмен | XCHG | 6/6 | 3/1,5 | 2/1,5 | 2/2 | 2/2 | 2/1 | 2/1 | 1/1 | 3/3 | 3/1,5 | |

| Логические операции | AND, (X)OR, NOT, TEST | 1/0,5 | 1/0,5 | 1/0,5 | 1/0,3 | 1/0,3 | 1/0,3 | 1/0,3 | 1/0,3 | 1/0,5 | 1/0,5 | |

| Простые сдвиги | SH*, SA*, RO* | 1/1 | 1/1 | 1/1 | 1/0,5-1 | 1/0,5-1 | 1/0,3 | 1/0,3 | 1/0,3 | 1/1 | 1/0,5-1 | |

| Сложение, вычитание | ADD, SUB | 1/0,5 | 1/0,5 | 1/0,5 | 1/0,3 | 1/0,3 | 1/0,3 | 1/0,3 | 1/0,3 | 1/0,5 | 1/0,5 | |

| Умножение, 32×32=32 бита | IMUL | 5/2 | 4/1 | 4/1 | 3/1 | 3/1 | 4-5/2 | 3/1 | 3/1 | 5/1 | 2/1 | |

| Умножение, 32×32=64 бита | 6/6 | 5/5 | 5/5 | 5/1,5 | 5/2 | 4/3 | 3/3 | 3/3 | 8/8 | 3/3 | ||

| Скалярный вещественный (x87) | Копирование | FLD | 1/1 | 1/1 | 1/1 | 1/1 | 1/1 | 1/0,5 | 1/0,5 | 1/0,5 | 1/1 | 1/1 |

| Условное копирование | FCMOV* | 9/9 | 2/2 | 2/2 | 2/2 | 2-4/2 | 1-6/5 | 1-4/4 | 1-4/4 | 2/2 | 2/2 | |

| Обмен | FXCH | 1/1¹ | 0/0,3 | 0/0,3 | 0/1 | 0/1 | 0/0,4 | 0/0,4 | 0/0,3 | 0/1 | 0/1 | |

| Сложение, вычитание | FADD, FSUB | 5/1 | 3/1 | 3/1 | 3/1 | 3/1 | 4/1 | 4/1 | 4/1 | 2/1 | 2/1 | |

| Умножение | FMUL | 5/2 | 5/2 | 5/2 | 5/2 | 5/1 | 4/1 | 4/1 | 4/1 | 4/2 | 4/2 | |

| Скалярный вещественный (SSE*) | Сложение, вычитание, SP | ADDSS, SUBSS | 5/1 | 3/1² | 3/1 | 3/1 | 3/1 | 4/1 | 4/1 | 4/1 | 2-3/1 | 2/1 |

| Сложение, вычитание, DP | ADDSD, SUBSD | 5/1 | 3/1 | 3/1 | 3/1 | 4/1 | 4/1 | 2-3/1 | 2/1 | |||

| Умножение, SP | MULSS | 4/1 | 4/1² | 4/1 | 4/1 | 4/1 | 4/1 | 4/1 | 4/1 | 3/1 | 3/1 | |

| Умножение, DP | MULSD | 5/2 | 5/2 | 5/1 | 5/1 | 4/1 | 4/1 | 4/2 | 4/2 | |||

| Векторный целочисленный (MMX, SSE*) | Копирование | MOVQ, MOVDQ* | 1/0,5 | 1/0,5 | 1/0,5 | 1/0,3 | 1/0,3 | 2/0,5 | 2/0,5-1 | 2,5/0,3 | 1/1 | 1/1 |

| Логические операции | PAND(N), P(X)OR | 1/0,5 | 1/0,5 | 1/0,5 | 1/0,3 | 1/0,3 | 2/0,5 | 2/0,5 | 2/0,5 | 1/1 | 1/1 | |

| Перепаковка | PACK*, PUNPCK*, PSHUF* | 1/1 | 1/1 | 1-2/1-2 | 1-3/1-2 | 1/0,5-2 | 2/0,5-2 | 2-3/0,5-2 | 2-3/0,5 | 1/1 | 1/1 | |

| Сложение, вычитание | PADD*, PSUB* | 1/0,5 | 1/0,5 | 1/0,5 | 1/0,5 | 1/0,5 | 2/0,5 | 2/0,5 | 2/0,5 | 1/1 | 1/1 | |

| Умножение MMX | PMUL* | 4/1 | 3/1 | 3-4/1 | 3/1 | 3/1 | 3/1 | 3/1 | 3/1 | 3/1 | 3/1 | |

| Умножение SSE | 5/2 | 3-4/2 | 3/1 | 3/1 | 3/2 | 3/1 | 3/1 | 3/1 | ||||

| Векторный вещественный (SSE*) | Копирование | MOVP* | 1/0,5 | 1/1² | 1/1 | 1/0,3 | 1/0,3 | 2/1 | 2/1 | 2,5/0,5 | 1/1 | 1/1 |

| Логические операции | AND(N)*, (X)OR* | 1/0,5 | 2/2² | 1/0,5 | 1/0,3 | 1/1 | 2/2 | 2/2 | 2/0,5 | 1/1 | 1/1 | |

| Перепаковка | UNPCK*, SHUFP* | 1/1 | 2-3/2² | 1-4/1-2 | 1-3/1-2 | 1/1 | 3/3 | 3/2-3 | 3/0,5 | 1/1 | 1/1 | |

| Сложение, вычитание, SP | ADDPS, SUBPS | 5/1 | 3/2² | 3/2 | 3/1 | 3/1 | 4/2 | 4/2 | 4/1 | 2-3/1 | 2/1 | |

| Сложение, вычитание, DP | ADDPD, SUBPD | 6/6 | 3/2 | 3/1 | 3/1 | 4/2 | 4/1 | 2-3/1 | 2/1 | |||

| Умножение, SP | MULPS | 5/2 | 4/2² | 4/2 | 4/1 | 4/1 | 4/2 | 4/2 | 4/1 | 3/1 | 3/1 | |

| Умножение, DP | MULPD | 9/9 | 5/4 | 5/1 | 5/1 | 4/2 | 4/1 | 4/2 | 4/2 |

¹ — в отличие от др. ЦП, не спаривается с другими командами x87 ↑

² — только для P III ↑

Сначала сделаем замечание насчёт разницы в неарифметических векторных командах (копирование, логика и перепаковка): все они делаются побитно, так что, по идее, нет разницы между логическим ИЛИ над целыми и вещественными любой разрядности и точности. Однако в некоторых ЦП (например, Core i) ФУ объединены в домены (не совпадающие с группировкой по портам), исполняющие команды только конкретных групп (например, целые скалярные), так что «вещественная логика» парадоксально может оказаться медленней «целочисленной». Нано и Атом к таким ЦП не относятся и начисляют штрафы только за некоторые межпортовые передачи.

И ещё — о вранье в официальных документах VIA. Авторы (надо полагать, Гленн Хенри в их числе) пишут, что 2-тактное вещественное сложение (тут и далее это относится и к вычитанию) в Нано быстрее 3-4-тактного у Intel, где это число зависит от точности. Так вот — все вышеуказанные ЦП делают любое вещественное сложение за одинаковое число тактов (5 у Атома, 3 у остальных ЦП Intel и 4 у AMD) вне зависимости от числа и типа элементов (кроме Атома с неконвейерными 6 тактами для ADDPD). Также пишется, что вещественное умножение тоже имеет самые низкие задержки среди всех x86-ЦП. Это дважды неправда и один раз не полная правда. По сравнению с ЦП Intel (особенно Атомом) Нано и впрямь д’Артаньян, но вот все ЦП AMD исполняют вещественные умножения двойной (да и вообще любой) точности за те же 4 такта, что и Нано. Причём K7/K8 исполняют в полноконвейерном режиме только скаляры, а K10 — и векторы; умножитель Нано в случае с двойной точностью (DP) даже для скаляров работает в полуконвейерном режиме.

Что касается одинарной точности (SP), можно вспомнить, что K6-2 исполнял векторные целочисленные (MMX) и вещественные (3DNow!) умножения даже за 2 конвейерных такта (2/1 по нашей метрике), работая при этом на приличной для своего техпроцесса частоте. Впрочем, так далеко идти не надо — все версии WinChip 2 самой Centaur также поддерживали 3DNow! и выполняли и SP-сложение, и SP-умножение с параметрами 2/1, а полное x87-умножение — 4/2. Т. е. по совокупности этих параметров WinChip 2 был даже чуть быстрее Nano.

Но кое-что интересное в новом умножителе всё же есть: он связан с сумматором шиной промежуточного результата повышенной разрядности для уменьшения ошибок округления, что используется в трансцендентных функциях типа синуса из поднабора x87. Слитое умножение-сложение (FMA) только готовится в новых дополнениях AVX у Intel и XOP (бывшее SSE5) у AMD. И хотя VIA уже готова, использовать повышенную точность в современных программах не получится, т. к. слитый моп для FMA макрослиянием пока не генерируется, а x87 давно устарел.

Таблица выше наглядно показывает реальные сильные и слабые места исполнительной части Нано. Вещественные ФУ срабатывают не медленнее (а чаще всего — быстрее) всех остальных ЦП. А вот векторные целочисленные команды хотя и быстрые, но исполняются лишь по одной. Между прочим, даже Pentium MMX, впервые среди x86 получивший SIMD-ФУ, уже умел исполнять 2 векторных команды за такт, обрабатывая таким образом те же 128 бит, что и сегодняшний Нано. Позора добавляет то, что CNA, как 486-й, даже пару скалярных копирований не мог делать одновременно. Да и целочисленные скалярные умножения тоже не на высоте (медленней — только Pentium). CNB частично исправил ситуацию, добавив в один из целочисленных конвейеров блок копирования, а в другой — регистр сдвига и 32-битный умножитель (что позволяет одновременно сделать вещественное и целое умножения, если последнее — скалярное и не 64-битное). Кроме того, удалены случайные 1-тактовые задержки при вещественном векторном сложении.

Теперь о делении и извлечении корня. Это редкие операции, а делитель — штука громоздкая не меньше умножителя, так что роскошь векторного делителя для Нано, как и Атома, не по карману (при том, что он во всех ЦП неконвейерный). CNA оснащён одним делителем-извлекателем для целых (кроме 64-битных делений, которые на всех ЦП очень медленно эмулируются) и вещественных всех точностей. В результате, например, операция вычисления корня выполняется над 4-элементным SP-вектором вчетверо дольше, чем над SP-скаляром, и даже чуть дольше, чем над 2-элементным DP-вектором. Чтобы не было так стыдно, в CNB основной делитель ускорен почти вдвое. Но главное — добавили ещё один вещественный скалярный делитель-извлекатель для SP (второй «малый» делитель есть и в Атоме). Это дополнительно вдвое ускорило упакованные SP-деления и извлечения. В результате новый Нано стал делить несильно хуже «больших ЦП», а вот корни извлекаются так же медленно, как и в Атоме.Кэши

Для начала сухие цифры:

- L1I и L1D — 64 КБ, задержка 4 такта;

- L2 — 1 МБ, задержка 24 такта;

- Все кэши имеют 64 байта на строку и 16-путную ассоциативность;

- Обе шины «L1↔ядро» — 128-битные, а «L2↔L1» — 64-битная.

VIA никогда не экономила на размерах L1, и в Нано, как и в предыдущие ЦП, поставила 64 КБ в оба первичных кэша. Но, в отличие от AMD, где 64 КБ также наблюдаются последний десяток лет, и особенно Intel, где оба L1 вдвое меньше (у Атома L1D даже 24 КБ), Нано обладает явным преимуществом — все его кэши 16-путные, что увеличивает частоту попаданий. И если для L2 это вполне ожидаемо, то для L1 это рекорд — AMD имеет 2 пути, в Атоме их 6, в остальных ЦП Intel — 8. Разумеется, на всё есть объяснение — одновременное срабатывание аж 16 компараторов в тегах для сравнения адресов кэша занимает изрядное время. Только L3 позволено работать на частоте, меньшей, чем у ядра — доступ к L1 и L2 более мелко нарезают на стадии конвейера, чтобы время срабатывания не стало ограничением увеличения частоты. Например, у Core i, которому надо за счёт технологии TurboBoost разгоняться до 3,5 ГГц и выше, доступ к L1 — 4 такта (так же было у «пожирателей частоты» P4E и IBM Power6), а у подавляющего большинства остальных современных ЦП, включая Atom, — за 3. По идее, если бы 16 путей у Нано срабатывали бы за 3 такта, в теории это означало бы невозможность разгона свыше ≈2,5 ГГц (на 65 нм), и пока он на такие высоты не метит — это допустимо. Однако VIA почему-то увеличила задержку на 1 такт…

Кстати, 24 такта для L2 — это тоже по-бегемотски; даже 65-нанометровые Core 2 тратили 14 тактов для доступа к 4 МБ L2 по 16 путям и при бо́льших частотах. А по разрядности шин Нано и вовсе отстаёт в 2–4 раза от всех, кроме Атома. Причём даже эти шины он не может загрузить полностью — каждые 8 байт читаются минимум за 1,6 такта из L2 и минимум за 3,7 из памяти. Запись в память ещё втрое медленнее.

Ещё один спорный момент — L2 эксклюзивен относительно L1. VIA (как и AMD) гордится, что это увеличивает общий объём данных, умещающихся во всех кэшах, а ещё упрощает их управление — L2 заполняется только удалёнными из L1 строками, т. к. при промахе в L2 данные из памяти грузятся сразу в L1. Но стоит ли это лишних задержек и милливатт при промахах в L1 (с заменой несохранённых строк) — ответа нет. Да и в многоядерных вариантах будет труднее отследить наличие нужных данных у соседних ядер, т. к. просматривать надо не L2, а все три кэша.

Куда детальней VIA рассказывает о своих предзагрузчиках — в Нано два алгоритма, следящих за линейными шаблонами чтения (без привязки к мопам) и статистикой промахов в L1D. Предзагруженные первым алгоритмом данные сохраняются в L1, а вторым — в отдельный буфер на 64 строки (т. е. 4 КБ), проверяемый одновременно с доступом в L1 — это увеличивает совокупную эффективность подсистемы памяти, т. к. предзагруженные второй схемой данные по своей природе имеют весьма короткую актуальность и больший риск промаха адресов.

Несмотря на отдельные порты запуска чтения и записи, 2-портовость самого L1D у Нано работает необъяснимо редко — и если 2-путному Атому один доступ в память за такт простителен (хотя даже у первых Pentium был 2-портовый L1D), то для 3-путного суперскаляра это явный тормоз. Более того, любая запись в кэш Нано в среднем занимает даже не 1, а 1,5 такта. Несколько исправляет ситуацию наличие аналога схемы «memory disambiguation» из Core 2/i — там она позволяет загружать данные в ядро до того, как точно станет известно, что их не перезапишут ещё не отставленные команды записи по своим пока невычисленным адресам. В Нано эта схема тормозит размещение команды чтения в резервации и предзагрузку данных для неё, если предсказывает совпадение с адресом незаконченной записи, для чего ведётся история предыдущих записей и совпадений.

Порты ST и LD имеют очередь записи на 16 16-байтовых слов (удерживающую данные до отставки всех предыдущих команд в программном порядке) и буфер слияния записей в основную память (Write Combine, WC buffer) на 6 64-байтовых строк. Сливать записи из L2 не надо, т. к. вытесняемые сроки и так перемещаются целиком, а вот для записи из ядра в L1 такая функция очень нужна и наверняка встроена в очередь записи. К ней также подключен блок STLF, который работает только в наиболее простых случаях, когда по адресу отставленной, но не выполненной записи читается не больший по размеру блок данных (если меньший — он дополняет считываемое из кэша слово) — иначе процессор замирает на 7, 11 и даже 33 такта. В CNB большинство штрафов уменьшено до 7 тактов (максимум — 18), но сам блок умнее не стал: ему далеко не только до чемпиона (в этом смысле) Core i, но и до Атома. Такой же прогресс наблюдается и при невыровненном доступе к памяти: «зверские» штрафы (18 тактов для чтения и 37 при записи) более чем вдвое дольше ожидаемых и имеющихся в др. ЦП (даже у Атома задержки по 16 тактов). Но CNA штрафуют пересечение и середины строки (каждые 32 байта), а CNB — только границы.

Нано имеет простую схему из пары TLB для кода и данных по 128 ячеек с 8-путной ассоциативностью, а TLB второго уровня нет. Для сравнения: TLB первого уровня в K10 имеют по 48 ячеек, а в Core i — 128/64 для L1I/L1D. Правда, у них есть ещё TLB L2 на 512 страниц (в K10 их даже два). А вот отсутствие TLB для 4 МБ страниц (2 МБ для 64-битного режима), возможно, подразумевает вечные промахи при обращении к ним. При промахе TLB сначала обращается в L2, куда затем вытесняет из себя «лишние» записи, на что тратится 53 такта. При невыровненном доступе с пересечением 4К-границы спекулятивная проверка в TLB сокращает задержку до 33 тактов.

Уникальным можно считать блок VSM — Volatile Secure Memory, энергозависимая защищённая память кода с собственным адресным пространством, обращения к которому никогда не дублируются на шину. (Возможно, это не блок, а один из режимов работы L2 — объём VSM не назван.) Смысл этой схемы прост — ЦП читает зашифрованный код из памяти, распаковывает его командами PadLock, записывает в VSM и исполняет. В теории это гарантирует, что незашифрованный код не выйдет за пределы ЦП, что увеличивает надёжность защищённого исполнения.Нано всякие нужны…

По традиции, отошлём читателя к списку моделей Нано в Википедии, который и обсудим. Вот главные платформы для Нано: для неттопов и дешёвых «нормальных» ноутбуков выпускаются модели L, а для чего-то ультра-портативного — линейка U. Ядро CNA получило номера моделей 1xxx и 2xxx, а новые CNB — 3xxx. Причём для последних VIA не указала значения TDP, упомянув в пресс-релизе лишь, что оно «на 20% меньше» CNA. Гадать не будем — доверять рекламе хитрых тайваньцев стоит не больше, чем любой другой рекламе.

Видно, что номера моделей проставлены каким-то особым методом, недоступным пониманию простых смертных. Что означает знак «+» рядом с частотой, тоже не объяснено, но можно предположить, что только у этих моделей активирована функция авторазгона (о ней ниже). А ещё в списке (на июль 2010-го) отсутствуют версии для встроенных применений Nano E — пока известен лишь их частотный диапазон (0,8–1,8 ГГц).

Все выпускаемые Нано размещены в корпусе типа NanoBGA2 (это название появилось ещё в 2005-м) размером 21×21 мм и полностью совместимы с предыдущими ЦП C7 и Eden. При анонсе VIA показала ещё один вариант корпуса размером всего 11×11 мм, что явилось бы рекордом для x86-ЦП, если бы такие процессоры реально появились в продаже…

Любопытно, что VIA не собирается в ближайшее время заменять все свои ЦП, хотя по всем техническим параметрам Nano лучше C7, а если не считать большего потребления — то и Eden. Тем не менее, к выходу Нано приурочен выпуск чипсета VX800 и его мобильной версии VX800U (отличия — в скобках):

- Однокристальный чипсет размером 33×33 мм;

- Графическое ядро — VIA Chrome9 HC3 на 250 (166) МГц с поддержкой DirectX 9.0 и Pixel Shader 2.0, аппаратным декодированием MPEG-2/4, DivX и VC-1 при разрешении Full HD и с выходами VGA и LVDS;

- Частоты FSB — 400–800 (только 400) МГц;

- До 4 ГБ в двух модулях DDR2-667 на одном канале;

- Контроллер Vinyl HD Audio с внешним кодеком — 8 каналов, 192 кГц, 32 бита;

- SATA-II — 2 порта, PCI-e — 1 разъём x4 и 2 x1 (всё это отсутствует в VX800U из-за их прожорливости);

- Интерфейс картовода для SD/MMC/MS;

- TDP — 5 (3,5) Вт.

Через год вышло обновление: VX855 с поддержкой DDR2-800, новым видеоядром Chrome9 HCM (включает декодирование H.264 и WMV9), TDP в 2,3 Вт и корпусом размером 27×27 мм. А в марте 2010-го анонсирован VX900 с поддержкой DDR3-1066, портами DVI, HDMI и DisplayPort, ускоренным PCI-e и другими дополнениями.

Флагманский 2-корпусный чипсет VN1000, выпущенный в 2009-м, получил поддержку DDR3-1066 (в отличие от VX900 — до 16 ГБ в двух каналах) и видеоядро VIA Chrome 520 с частотой ок. 500 МГц, 32 универсальными потоковыми ядрами и 4 текстурными блоками, поддержкой DirectX 10.1, Pixel Shader Model 4, OpenGL 3.0 и OpenCL 1.0 (для GPGPU), ускорения Blu-ray и WMV-HD (помимо остальных) и вторым портом HDMI. Южным мостом к VN1000 идёт VT8261 с 4 портами SATA-II и 12 USB 2.0 — остальное неизменно. Весь чипсет просит 12 Вт.Экономия

Отбросив ожидаемую шелуху про «самый экономный» (и это на 65 нм) и прочие «новейшие достижения», посмотрим на разницу между Нано и другими мобильными ЦП. Поблочное управление тактированием в зависимости от загрузки и смена P-состояний для всего ядра не новы даже для VIA. Зато умножитель в Нано устроен так же, как коробка передач с двойным сцеплением, когда-то изобретённая для гоночных болидов: по сути это 2 умножителя для целых и полуцелых множителей. При работе одного второй настраивается на множитель на 0,5 больше или меньше текущего в зависимости от ожидаемого «вектора ускорения». Это занимает приличное время, т. к. умножитель с ФАПЧ (PLL) суть аналоговая схема. Но т. к. это делается заранее, в нужный момент остается только изменить напряжение питания на минимальный шаг и быстро переключиться с одного умножителя на другой — при этом они меняются ролями, а главное — ЦП продолжает непрерывную работу. Цикл повторяется, пока не будут достигнуты целевые частота и напряжение. Для сравнения — прыжки на несколько P-состояний за раз могут потребовать сотни микросекунд простоя ядра. Нельзя точно сказать, что др. ЦП не имеют ничего похожего, но VIA рассказала об этом первой :)

Другое номинальное «впервые» — автоподстройка макс. частоты и мин. напряжения в зависимости от фактической температуры. VIA приводит такой пример: Нано на 2 ГГц требует 1,1 В питания для стабильной работы при максимально допустимой температуре в 85 °C. Допустим, встроенный термодатчик показывает 60 °C — это даст возможность либо уменьшить напряжение до 1 В, либо увеличить частоту до 2,2 ГГц (превысив номинал), в зависимости от требований программы. Напомним, что в начале 2008-го об Intel TurboBoost никто пока не знал.

Впрочем, реальность, как и с Атомом, не даёт соврать — модель L2100 на 1,8 ГГц требует 1,196 В, а L2200 на 1,6 ГГц — 1,116 В. Любопытно, что VIA заявляет, будто все Нано тестируются при температурах 5–85 °C, и для L2100 отбираются ядра, прошедшие тест при 1,1 В. Видимо, у VIA есть причина на всякий случай завысить напряжение… Кстати, максимально допустимую температуру можно назначить программно, и ЦП её не превысит — это поможет «утихомирить» шумный кулер (что совсем не лишнее для домашнего устройства), а также защитить от перегрева близкорасположенные к радиатору процессора компоненты (то что надо для тесного корпуса).

Как и Атом, Нано поддерживает энергосостояния C1—C4 и имеет специальную память для сохранения статуса конвейера в состоянии C6, когда остальные блоки отключаются от всех герц и вольт (правда, C6 был недоступен в первом степпинге CNA). Включенным остаётся примерно 1 млн. транзисторов, потребляющих 0,1-0,2 Вт для «ультранизковольтовых» (гм…) моделей и 0,2-0,5 Вт для «обычных». Это меньше, чем у мобильных Core 2 на 45 нм, но до Атома далеко… Ну а 5–25 Вт при полной нагрузке — цифры и вовсе неприличные для ЦП с таким названием. Хотя для целевых применений вполне подойдёт.Разбор полётов

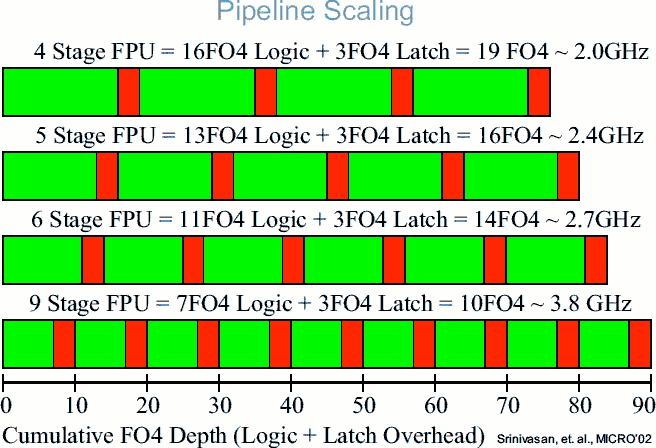

Сначала разберёмся с деталями рекордно низких задержек ФУ. Как уже было описано в статье о методах ускорения процессоров, «нашинковав» конвейер на большое число мелких стадий, мы упростим каждую стадию и, таким образом, ускорим весь конвейер. Допустим, это как раз то, что нам надо. Но тут подкрадывается проблема — буферные регистры-защёлки между стадиями тоже занимают некоторое место, увеличивают время срабатывания и потребляемую мощность.

Сделанное IBM исследование производительности новейшего на тот момент (2002 г.) техпроцесса 180 нм показывает число логических вентилей (измеренное стандартной метрикой FO4), которые должны сработать в каждой стадии вещественного конвейерного ФУ (включая буферы), в зависимости от числа стадий — а также результирующую макс. частоту. 4-стадийный дизайн работает вдвое медленнее 9-стадийного, занимая на 15% меньше места. Теперь посмотрим на потребление:

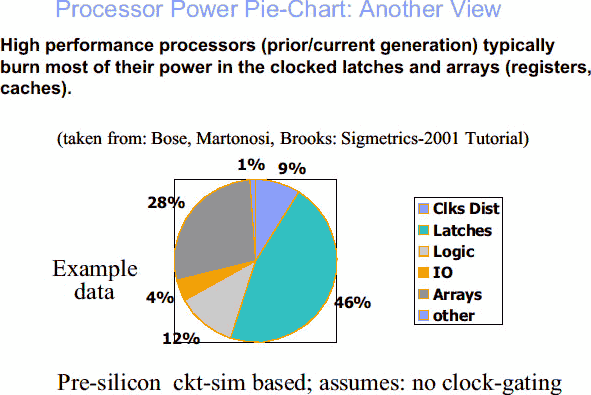

Тут всё куда хуже. Оказывается, в наиболее высокопроизводительных длинноконвейерных ЦП (типа IBM Power и Intel Pentium 4) почти половина мощности ядра уходит на буферы, срабатывающие каждый такт после каждой стадии, тогда как далеко не все транзисторы самих стадий работают в каждый момент даже при полной загрузке конвейера. Лишь 12% приходятся на логику, включая ФУ, и ещё 28% — на двухмерные регулярные структуры типа кэшей. Высокочастотная распределительная сеть также весьма прожорлива — 9%.

Теперь становится ясно, почему VIA стремилась сделать не просто «не очень высокочастотный» ЦП, а ещё и не очень конвейеризированный. Со всем конвейером это сделать не получится (современный OoO-движок вряд ли может быть короче полутора десятков стадий), но можно попытаться с ФУ, тем более что именно они являются са́мой прожорливой частью ядра. Обратная сторона — максимальная частота, которая при 2 тактах на вещественное сложение и 3–4 на умножение при техпроцессе 65 нм вряд ли поднимется выше 2,5 ГГц. Но и столько пока не требуется. Зато будет полезно сэкономить чуток площади под буферы.

Площадь CNA — 60 мм², а CNB — 63 мм², из чего можно заключить, что «трёхтысячники» — это «тщательно обработанная напильником» первая версия, в которой многие нововведения второй наверняка уже были. Более того, Хенри не без гордости заявил, что инженеры стали «бесконечно мудрее», исследовав первые кремниевые образцы того, что ещё недавно моделировалось в цифре, и сразу найдя множество мест для улучшения. Число транзисторов для CNB неизвестно, а для первых Нано его объявили как 94 млн. Несмотря на техпроцесс 65 нм, обе версии всё равно вдвое больше 90-нанометрового C7. Т. е. одновременно дешёвый, быстрый и энергоэффективный чип VIA не могла получить по определению, тем более что во избежание бо́льших токов утечки пришлось использовать не самые мелкие транзисторы из доступных на 65-нанометровой технологии.

Самое время составить обзорный список того, что изменилось в CNB относительно CNA. Это полезно для определения, чего достигли «бесконечно помудревшие» микроархитектурщики за 1,5 года работы, почти не увеличив площадь ЦП:

- Макрослияние допустимо почти с любым условным переходом, добавлено слияние НОПов (с предыдущей командой) и микрослияние мопов записи в память;

- Исполнение SSE 4.1, причём почти всё конвейеризировано;

- Поддержка виртуализации;

- Ложные взаимозависимости при очистке регистров обнаруживаются в большем числе случаев;

- Исправлена блокировка портов неслитыми НОПами;

- Добавлены скалярные целочисленные ФУ: второй блок копирования-обмена (в т. ч. условного), второй скалярный сдвигатель и рекордно быстрый 32-битный умножитель;

- Деление ускорилось в 1,5–4 раза, извлечение корня для векторных SP-чисел — вдвое;

- Ускорен шифроблок PadLock, добавлены команды AES-NI;

- Невыровненный доступ штрафуется вдвое реже (через 64 байта);

- При несрабатывании STLF штрафы в 1,5–5 раз меньшие;

- TDP «на 20% меньше» (?..).

Работа над ошибками явно проделана не зря — собственно, именно таким Нано и должен был выйти с самого начала, но задним числом все умны. Тем не менее, многие недостатки всё ещё остались неисправленными. Главный из них — векторные целочисленные операции делаются лишь в одном порту (соответственно, максимум одна за такт), включая простейшее копирование регистров. Даже Атом в этих командах вдвое быстрее Нано, а «большие» ЦП простые векторные операции выполняют и по три за такт.

На такое Нано не хватит транзисторов, а вот третье скалярное АЛУ вполне пригодится: эволюция 3-путных ЦП обеих фирм-лидеров демонстрирует, что целые скаляры — это первые команды, достигшие темпа 3 за такт. Дело не только в большой востребованности, но и в простоте реализации — добавить третье 64-битное АЛУ куда дешевле по площади и ваттам, чем третье 128-битное. Это тем более удобно сделать в Нано — посмотрите ещё раз, как мало места занимают его целочисленные ФУ (на самом деле — больше указанного, т. к. нижняя граница проведена на фото выше фактического начала тракта). Небольшая добавка увеличит пиковую скорость по наиболее частым командам в полтора раза.

По вещественным числам единственная ложка дёгтя — полуконвейерное DP-умножение, даже для скаляров. Для достижения не только максимальной скорости, но и энергоэффективности все часто используемые ФУ должны быть полноконвейерными для всех своих команд. Так что вместо добавления второго делителя полезней было бы улучшить умножитель.

Рекомендуемые дополнения обозначены в таблице тактов ФУ тёмно-зелёным цветом — при улучшении (уменьшении) цифр в этих клетках они станут не хуже, чем у лидеров, хоть и не перейдут в статус «синих» (лучших в своём классе). Что, разумеется, не отменяет более срочное исправление «красных меток». Из остального желаемого:

- Предсказатель может быть улучшен для случаев более двух переходов в 16-байтовом блоке, а также для совершения перехода быстрее 1 раза за 3 такта;

- Желательно макрослияние умножений-сложений;

- Буферу мопов после декодера полезна функция распознавания и блокировки цикла. Скорости это не добавит, т. к. фронт конвейера у Нано и так силён, а вот энергоэкономия при исполнении мелких циклов будет существенная;

- Отправка мопов при заполнении резерваций портов I1 и I2 может быть исправлена;

- Перепуск данных между портами избыточно штрафуется;

- А штрафов регистров-указателей не должно быть вообще;

- L1D должен стать по-настоящему 2-портовым (хотя бы как «1 чтение + 1 запись») и быстрым (с уменьшёнными до 1 такта пропуском и до 3 тактов задержкой);

- Штрафы невыровненных доступов и блока STLF должны быть уменьшены;

- Следует кардинально поднять ПС памяти, особенно при записи.

Теперь дела внеядерные. Очевидно, что без скорейшего перехода на новые техпроцессы в мобильном мире делать нечего. Если же без потери экономии хочется и гигафлопсами померяться, тут без многоядерности не обойдёшься. Вон, коллега Атом с самого начала физически бывает 2-ядерным, да ещё и гиперпоточным. Кстати, а не будет ли для Нано полезна SMP? Хотя у него есть OoO, 2-поточность проста в реализации. Пускай она принесёт не более 15%, но и ради этого стоит попробовать хотя бы проверить. Между прочим, эти прелести (кроме SMP…) VIA анонсировала ещё в 2008-м, заявив об ожидаемой готовности монолитных 2-ядерных Нано к лету 2010-го. А когда это лето настало, VIA показала лишь прототип на 65 нм, пообещав, что в массовый выпуск «двухнановые» процессоры пойдут лишь к концу 2010-го, зато сразу на 40 нм (производства TSMC).

Надо поднять вопрос и о размере кэша L2. Дело в том, что наши недавние тесты AMD Athlon II X2 215 показали, что эта модель, единственная из всех Athlon II X2 имеющая 0,5 МБ L2 на ядро, показывает производительность лишь на 3–4% меньше одночастотной модели с 1 МБ L2 — а ведь ядро K10 куда серьезнее (чем Нано) по вычислительной мощности, а значит, и по потребности в быстром кэше. Учитывая одинаковые размеры их кэшей L1, можно сделать вывод, что Нано запросто мог бы обойтись и половиной своего L2, а примерные подсчёты говорят, что так можно сэкономить 10–12% площади. Кстати, странно, что VIA не выпускает дешёвые «СелеНано» с отключенной половиной L2, если при производстве там обнаружены дефекты — как это делают остальные фирмы.

Для 2-ядерного же кристалла можно поступить умнее: скопировать подход Core 2, где пара ядер имела общий L2 с контроллером — тут как раз полный мегабайт и понадобится, а при 1-поточном исполнении он будет весь доступен активному ядру, да ещё и на площади второго контроллера сэкономим. Однако раздельные кэши хороши тем, что доступ к ним может быть одновременный. Исправить ситуацию поможет подход Core i — там L3 разделён на банки по 2 МБ со своими тегами и портами доступа, а к ядрам они подключены через 2-направленную кольцевую шину. Для 2-ядерного Нано схема упрощается: поставив два банка по 0,5 МБ и по паре шин до каждого ядра, можно получить 2-поточный доступ к L2 с вероятностью 50%, когда каждое ядро читает/пишет либо только свой банк, либо только чужой.

Более того, можно пойти ещё дальше и выпустить 2-кристальные 4-ядерные Нано а-ля Core 2 Quad — если архитектура окажется достаточно масштабируемой. Читатели могут вспомнить наши героические попытки составления классификации x86-процессоров, согласно которой текущая 1-ядерная версия Nano получила то же поколение 7+, что и многоядерный Атом, а значит, переход к многоядерности доведёт Нано до 8-го поколения, что уже на уровне Core 2/i и K8/K10 (опять же — в рамках нашей классификации).

Что ещё успели сделать конкуренты с начала 2008-го? Разумеется, интегрировали в процессор почти всё! Для Нано идеально подойдёт устройство Core i3/i5: корпус с чипами северного моста и собственно процессора, 1- или 2-ядерного. Так можно и место сократить, и частоту FSB поднять (если это как-то скроет позорные показатели ПСП), и чуток ватты и доллары сэкономить. Более того, у VIA уже есть такой 2-кристальный продукт — это CoreFusion. Правда, имеющиеся версии имеют размер 53×37 мм и сильно устарели начинкой…

VIA CoreFusion

Но главное даже не это. Допустим, VIA прочтёт все наши дилетантские рекомендации, возьмёт под козырёк (клиент автор всегда прав! :) и выпустит интегрированный Нано с парой улучшенных ядер и общим L2. Но стоила ли вообще вся внеочередная 3-путная игра мобильных свеч? Снова сравним с Атомом: число транзисторов всего 1-ядерного чипа, ядра + кэшей L1 и только ядра — 47, 14 и 9 млн. соответственно. Эти же цифры для Нано (примерно) — 94, 30 и 19. И вот интересно — даст ли одно ядро даже обновлённого Нано такую же скорость, что и 2-ядерный 4-поточный Атом (который на данный момент уже разогнался до 1833 МГц — у модели D525) с тем же общим числом транзисторов? Если нет, то VIA придётся крыть чем-то ещё. Это не массовость (плат и готовых устройств с Нано днём с огнём не найдёшь, а в России их вообще никто не продаёт), не энергоэффективность (она у Атома явно лучше), не цена (см. начало статьи)… Тогда зачем это всё? А ведь времени что-то исправить у VIA осталось не так много — купленная у Intel 10-летняя лицензия на выпуск х86-ЦП заканчивается в 2013-м, и кто знает, за какую цену её захотят продлить, особенно, если новые Нано таки окажутся удачными…

И последнее: дорогие друзья из VIA и Centaur! Если вы это читаете — что бы вы ни сделали, перестаньте, наконец, мухлевать в документации! Мы же всё равно вас разоблачим! :)

За основу для иллюстраций взяты материалы сайтов brightsideofnews.com, hotchips.org, legitreviews.com и VIA.

Тут оригинальная статья заканчивалась, но оказалось, что VIA вложила под капот Nano ещё одну тёмную лошадку. К архитектуре это не имеет прямого отношения и вполне могло появиться ранее в других процессорах — более того, возможно даже и появилось, но именно у Нано эту особенность удалось не просто обнаружить, но и использовать для интересного исследования, которому посвящена отдельная статья.